Introduction to Virtualization Technology.

64-bit Machine Language Instruction Format.Protected Mode Interrupts and Exceptions.32-bit Machine Language Instruction Format.If you re looking for a comprehensive book designed to bootstrap you up quickly on virtually all aspects of the x86 32/64-bit Instruction Set Architecture (ISA), we respectfully ask you to consider this book. X86 INSTRUCTION SET ARCHITECTURE TOM SHANLEY SOFTWAREProtected Mode Software Architecture extends MindShares coverage of x86. This book focuses on those shared attributes (it does not cover those areas where the two companies have chosen widely divergent solutions which, by definition, fall outside of the ISA specification). Part Two: Register Set and Real Mode provides an overview of Real Mode operation.

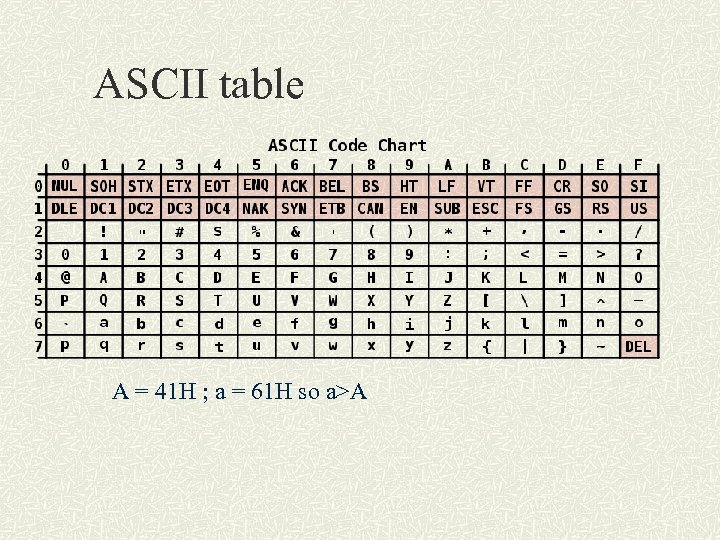

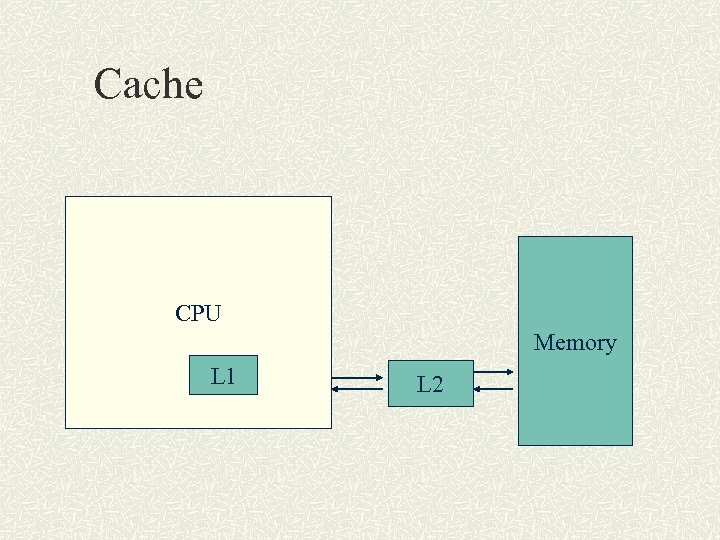

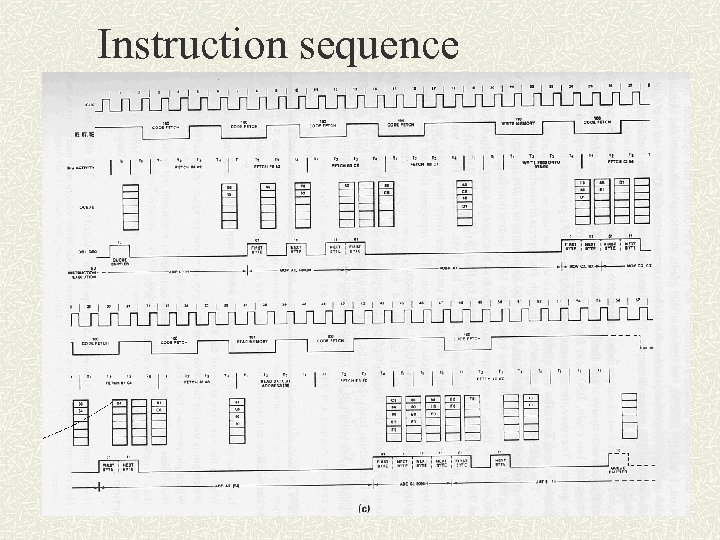

With the exception of some small deviations and differences in terminology, all Intel and AMD x86 processors share a common ISA. ADD EAX, 242424h 63 31 15 7 0 63 31 15 7 0 The upper 32 bits are cleared when Performing a Dword operation.The Instruction Set Architecture, or ISA, is defined as that part of the processor architecture related to programming, including the native data types, instructions, registers, addressing modes, memory architecture, interrupt and exception handling, and external IO.The operand sizes must match on most x86 instructions Scribd is the worlds largest social reading and publishing site. Understand the CPUs fetch-execute cycle Recall the ways memory is. X86 INSTRUCTION SET ARCHITECTURE TOM SHANLEY PDFADD R9W, EAX You cannot perform a byte operation using a high register (AH, BH, CH, DH) and one of the new registers (R8B – R15B). TomShanleyx86InstructionSetArchitecture.pdf - Free ebook download as PDF File (.pdf), Text File (.txt) or read book online for free. Knowledge of the x86 general registers Awareness of the x86s instruction-set.General-Purpose Registers (GPRs) R8D (“D” means a Doubleword access) Dword = 4 bytes R8W (“W” means a Word access) Word = 2 bytes R8W (“B” means a Bord access) Quadword = Qword = 8 bytes General-Purpose Registers (GPRs) (Accumulator) (Base) (Counter) (Data) Instruction Composition Average instruction size: 32-bit code: 3.4 bytes 64-bit code: 3.8 bytes IRET / 1 / 0 IP DEC CX CX = 2 LOOP Lable1 JNZ Label 1.The Instruction Set Architecture, or ISA, is defined as that part of the processor architecture. Here is a small subset of the x86 instructions related to program flow: Tom Shanley Published 31 January 2010 Computer Science.DX : AX SIMD operations (Single Instruction Multiple Data) Upper 16 bits Lower 16 bits.SQRTPS MMX instructions x87 instructions.A small sampling of the general-purpose and floating-point x86 instructions are shown below: Find x86 Instruction Set Architecture by Tom Shanley - Biblio.live is open March 24MaShop our first-ever virtual book fair with exclusive books, art, ephemera, and more at every price point.MOV, Note: intel syntax (destination, source).Introduction to Intel x86 Assembly, Architecture, Applications, & Alliteration. MOV, SI √ MOVS, moves data from one memory location to another tom shanley, x86 instruction set architecture: comprehensive 32- and 64- bit.MOV, BX move register data to memory.MOV BX, AX move ax register to bx register.MOV SI, 7000h move immediate to register.Here are a few variants of the MOV and ADD instructions as examples:

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed